模型机的总体设计

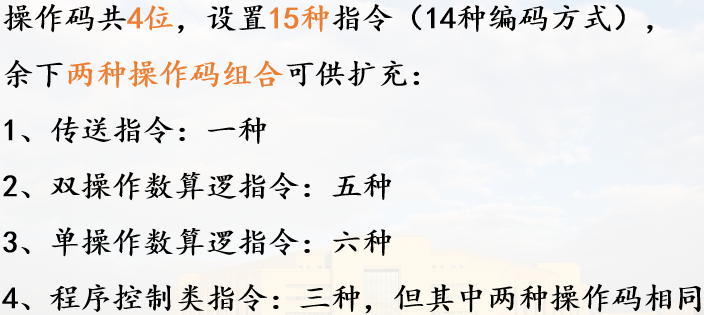

模型机指令系统

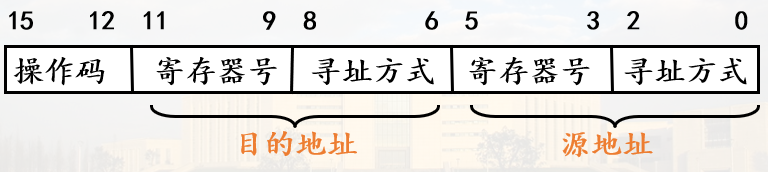

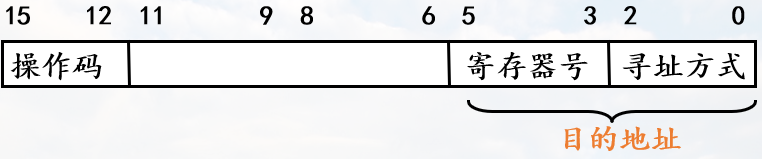

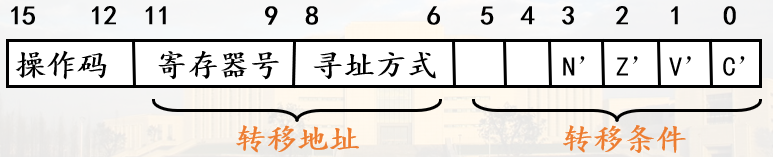

- 指令格式

- 双操作数指令

- 单操作数指令

- 转移指令

- 双操作数指令

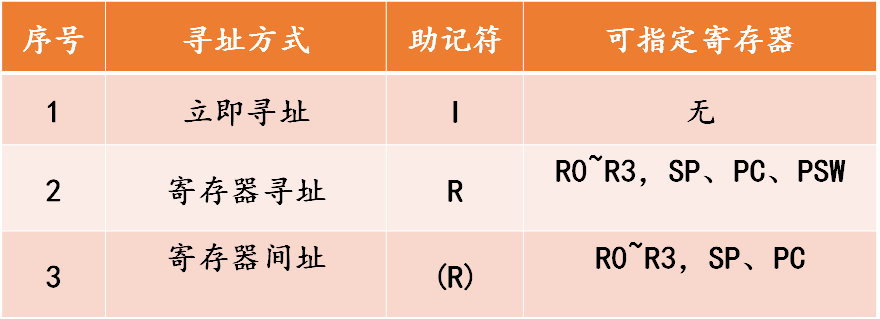

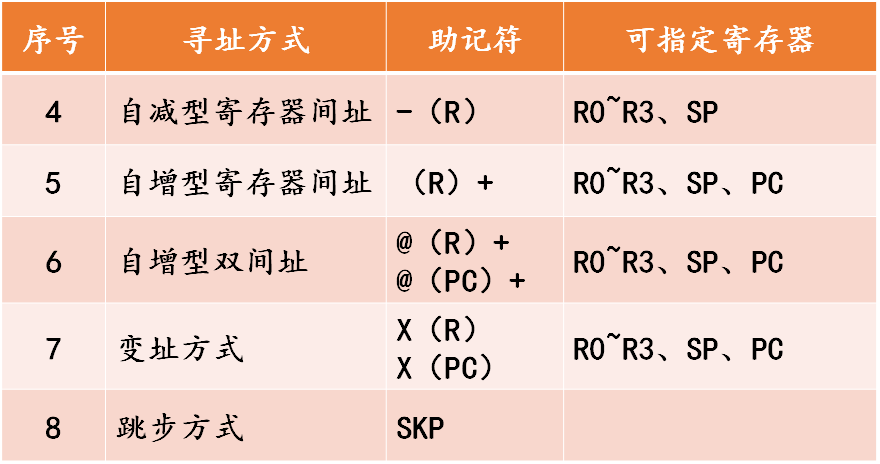

- 寻址方式

- 操作类型

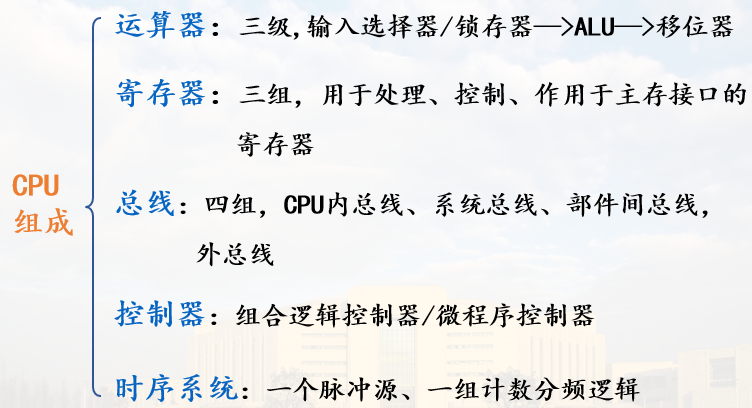

CPU的组成

运算器

- 输入选择器/锁存器

选择数据来源,送入ALU进行运算处理,或借道ALU进行传送。数据来源有:R0~R3、C、D、PC、SP、PSW、MDR。 - ALU部件

作各种算术,逻辑运算;由微命令M,S0,S1,S2,S3,C0选择操作功能。 - 移位器

作直接传送、左移、右移;由微命令实现直接、左、右移。

寄存器设置

- 用于处理的寄存器:通用寄存器、暂存器

- 通用寄存器组

一组可编程访问的寄存器。在指令系统中为这些R分配了编号,有:R0~R3,PC,SP,PSW。 - 暂存器

用户不能直接访问的R,用来暂存信息,在指令系统中没有为它们分配编号,有C、D。 暂存器C:从主存中读取源操作数或源操作数地址时,使用它。 暂存器D:从主存中读取目的作数或目的操作数地址时,或中间运算结果时,使用它。

- 通用寄存器组

- 用于控制的寄存器:指令寄存器IR、程序计数器PC、 程序状态字寄存器PSW

- 指令寄存器IR

用来存放现行运行指令,它的输出是产生微操作命令序列的主要逻辑依据。 - 程序计数器PC

PC提供后继指令地址,并送往与主存器相连接的地址寄存器(MAR)。 - 程序状态字寄存器PSW(program status word)

PSW的内容就是表现的现行程序的状态。 包括: 特征位:进位C、溢出V、零Z、负N,允许中断I等; 编程设定位。

- 指令寄存器IR

- 用作主存接口的寄存器:地址寄存器MAR、数据缓冲寄存器MBR(MDR)

CPU访问主存时,首先送出地址码,然后送出/接收数据,需:

A.当作用在MAR上的微命令EMAR为低电平时,MAR输出呈高阻态,与地址总线断开;

B.当作用在MAR上的微命令EMAR为高电平时,MAR输出其内容(地址信息)送往地址总线;- 地址寄存器MAR

读取指令/存取操作数/操作数地址时,CPU先将地址信息送入MAR,再由MAR经地址总线送往主存M,找到相应的主存单元。 - 数据缓冲寄存器MBR(MDR)

由控制命令R/W决定传送方向。

R:由主存单元->数据总线->MDR

W:由MDR->数据总线->数据单元

- 地址寄存器MAR

总线

- 定义

是一组能为多个部件分时共享的公共信息传送线路,及相应的控制逻辑。

数据通路结构:数据传送结构,它是CPU总体结构的核心问题。 总线:是一组能为多个部件分时共享的公共信息传送线路,及相应的控制逻辑。 - 总线类型

① CPU内总线: 模型机中是一组单向数据传送总线,是连接运算器、寄存器等CPU内部部件的总线。

② 部件间总线: 芯片间的连接总线,包含地址线与数据线两组。

③ 系统总线: 作用是计算机系统内各大部件进行信息交换的基础,分:地址总线AB、数据总线DB、控制总线CB

④ 外总线: 一台CS与其它设备相连接的总线。

时序系统

产生时序信号的部件称为时序发生器或时序系统,它由一个振荡器和一组计数分频器组成。

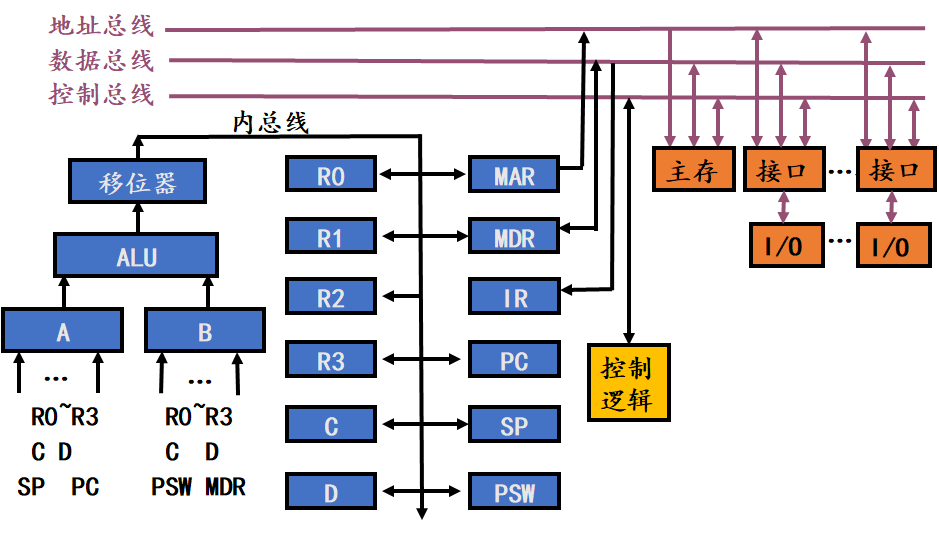

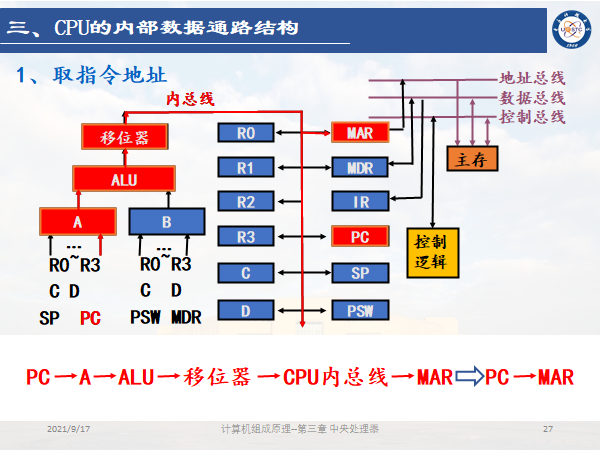

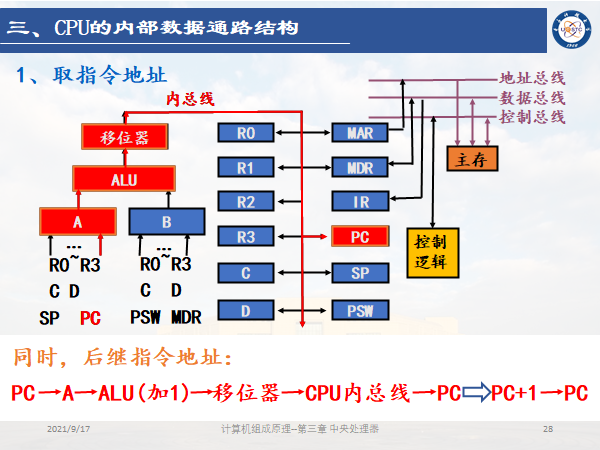

CPU的内部数据通路结构

模型机如何以内总线为纽带建立各部件间的数据传送通路,即CPU内部数据通路结构,这是CPU组成的核心问题。

模型机的结构为:单组、单向内总线、分立寄存器结构。

模型机数据通路框图

- 可编程寄存器

R0~R3通用寄存器(000,001,010,011)、SP(100)堆栈指针、PSW(101)程序状态寄存器、PC程序计数器 - 指令寄存器IR

用来存放现行运行指令,它的输出是产生微操作命令序列的主要逻辑依据。 - 暂存器

C、D约定从主存中读源操作数、操作数地址时用C;从主存中取目的操作数、操作数地址或暂存时,用D - 主存接口寄存器MAR、MDR(MBR)

- 地址寄存器MAR

读取指令/存取操作数/操作数地址时,CPU先将地址信息送入MAR,再由MAR经地址总线送往主存M,找到相应的主存单元。 - 数据缓冲寄存器MBR(MDR)

由控制命令R/W决定传送方向。

R:由主存单元->数据总线->MDR

W:由MDR->数据总线->数据单元

- 地址寄存器MAR

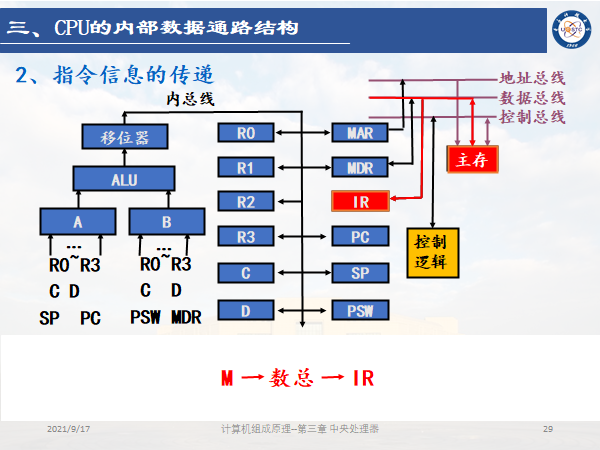

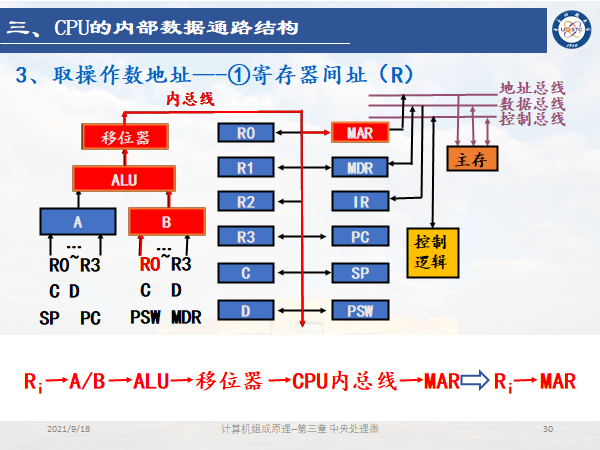

各类信息的传送路径

- 取指令地址

- 指令信息的传递

- 取操作数地址—①寄存器间址(R)

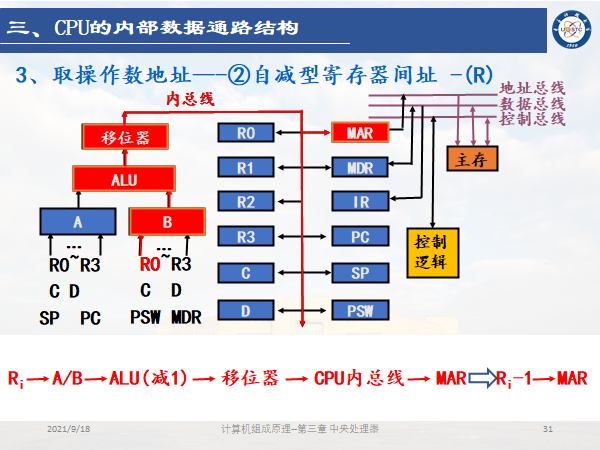

- 取操作数地址—②自减型寄存器间址 -(R)

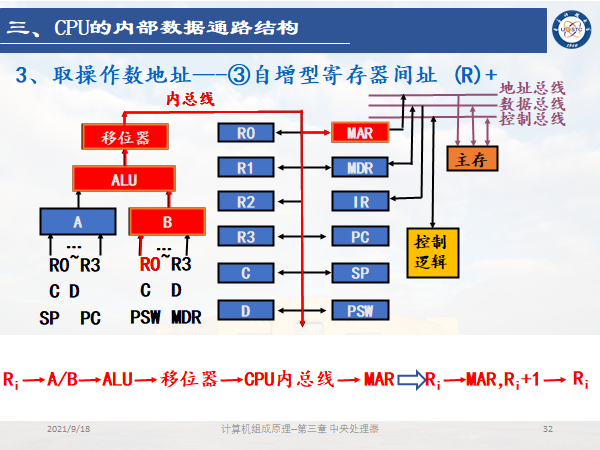

- 取操作数地址—③自增型寄存器间址 (R)+

两步走

微命令设置

- 数据通路操作

1) ALU输入选择: Ri→A,Ri的取值:R0—R3,C,D,PC,SP Ri→B,Ri的取值:R0—R3,C,D,MDR,PSW 2) ALU功能选择: S0—S3,C0,M (6位线) 3) 移位器功能选择: 00:直传DM、01:左移SL、10:右移SR、11:高低字节交换EX (2位线) 4) 分配脉冲(打入到寄存器中的脉冲): CPR0—CPR3, CPC,CPD,CPMDR,CPMAR,CPPSW, CPPC,CPSP - 访存操作相关的控制信号(系统总线及主存有关的微命令)

EMAR(输出到AB)、EMDR(输出到DB)、SMDR(DB到MDR)、 R(M到CPU)、W(CPU到M)、SIR(M到IR) (1)读入CPU:EMAR、R、SMDR(除指令以外),或SIR(指令) (2)写入M:EMAR、EMDR、W

主机与外部的数据通路 与 信息传送控制方式

主机与外设的连接模式:辐射型、总线型、通道型

对信息传送的控制方式:直接程序传送方式、程序中断方式、直接有储器访问方式

主机与外围设备的连接方式

- 辐射型

主机与各外围设备间有单独的数据通路;速度较快,**但**不易扩展。 - 总线型

各外设通过各自接口直接与公共的系统总线相连;结构简单,易扩展,**但**如果整个系统只有一组系统总线时,信息吞吐量有限,且速度较慢。 - 通道型

采取一种称为多种连接模式的部件去连接外设,这种部件称为通道;并行能力强。

信息传送的控制方式

直接程序传送方式

定义:CPU直接利用I/O指令程序实现I/O传送,在外设工作期间, CPU不执行与I/O无关的操作。

主机状态:CPU处于查询—等待—执行状态。

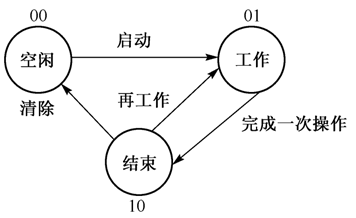

外设状态:在外设接口的状态字中设置两位表状态。空闲——外设不工作,00 工作(忙)——外设置在执行操作,01 结束(完成)——外设完成一次操作,10特点:CPU不能与外设并行地工作,因而CPU利用率低,并且CPU不能响应来自外部的随机请求。

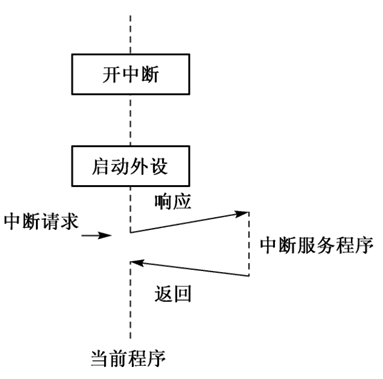

程序中断方式

定义:CPU暂停执行现行程序,转去执行中断程序,以处理某些随机事态,并在处理完毕后自动恢复原程序的执行。

实质:程序的切换过程。包括将断点,有关状态信息(PSW)压栈保护起来,然后根据中断号,从中断向量表中得到中断服务程序的地址,送入PC中。(这一切是硬件实现的,称为隐指令)

特点:随机性

软件组织与程序安排:将系统中接收的中断请求编制成中断服务模块存入主存,并将其入口地址写入中断向量表。

硬件组织:

CPU方面:在PSW中设置一个中断位;在模型机中,外部请求只有IREQ0—IREQ7,因此在CPU内还应设置一个判优逻辑。

接口方面:设置了中断接口。

特点:可以处理随机的复杂事态,但程序的切换需花费一定时间,因此,其适用范围是中低速I/O操作与随机请求。

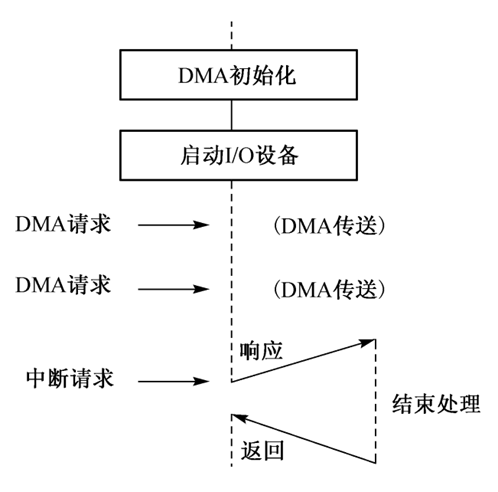

直接存储器存取(DMA)方式

定义:直接依靠硬件在主存与I/O设备进行简单成批数据传送的一种工作方式,在传送期间不需CPU的程序干预。

实质:暂停执行程序。不存在断点,现场的保护,速度很快。

程序组织与DMA初始化:在进行DMA传送前,应对DMA控制器进行初始化,主要初始化以下三个信息:

送出控制字:操作类型(输入或输出),外设地址;

送出主存缓冲区首址:传送或接收数据的起始地址;

送出交换量:DMA是批量传送的,传送的数据块数目。

硬件组织:由DMA控制器控制管理DMA传送。

CPU方面:在CPU的时序系统中,设置专门的DMA周期。在此周期,总线由DMA控制。每当系统总线周期结束(完成一次总线传送)时,CPU对总线控制权转移作出判断,是继续由DMA控制器掌管,还是CPU收回其控制权,恢复正常程序执行。

接口方面:设置DMA控制器与接口。

特点:适用于高速外设与主存之间的简单批量数据传送。

时序控制方式 与 时序系统

时序控制方式

- 同步控制方式

定义:如果各项操作与统一的时序信号同步,称为同步控制。

时间分配(基本特征):同步控制方式的基本特征是将操作时间划分为许多时钟周期,周期长度固定,每个时钟周期完成一步操作。

同步定时:在许多操作中需要严格地同步定时,如同步打入脉冲。

各部件间的协调:在CPU内,一般采用由CPU提供的统一时序信号来控制部件间信息的传送的。

特点:时序关系比较简单,在时间安排利用上可能是不经济的。 - 异步控制方式

定义:异步控制是指各项操作按其需要选择不同的时间,不受统一的时钟周期的约束;各操作之间的衔接与各部件之间的信息交换采取应答方式。

时间分配(基本特征):没有统一的节拍划分与同步定时脉冲,但存在着申请、响应、询问、回答一类的应答关系。

主从设备的概念:申请使用总线,并获得批准后掌管总线控制权的设备,称为主设备,否则为从设备。

特点:时间紧凑,能按不同部件,设备的实际需要分配时间,实现异步应答所需的控制比较复杂。 - 实际应用中的一些变化

在CPU或设备的内部普遍采用同步控制方式;对连接CPU、主存、外设的系统总线,有的采用同步,有的采用异步控制,但多采用异步控制。在实际应用中,同步控制甚至引入异步应答关系。

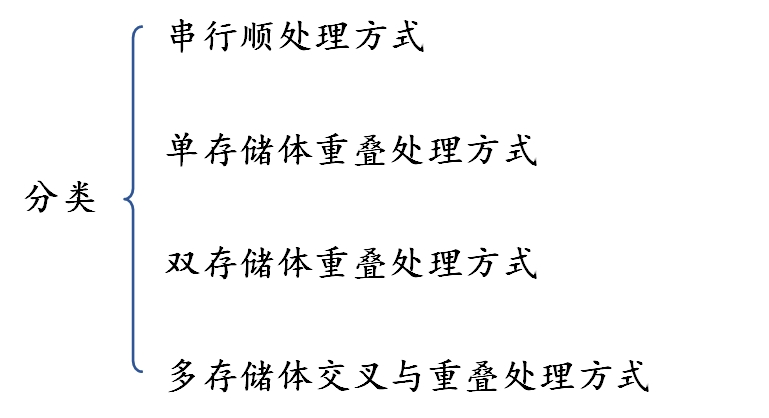

指令序列间的衔接方式

同步控制的时序系统

定义及组成

时序系统:产生节拍,脉冲等时序信号的部件,称为时序系统。

时序系统的组成:一个振荡器(产生脉冲源);一组计数分频逻辑

时序划分层次

指令周期:读取并执行一条指令所需的时间,称为指令周期。一般不作为时序的一级。

CPU工作周期:在指令周期中的某一工作阶段所需的时间,称为一个工作周期。一般不同(FT、ST、DT、ET)。

时钟周期(节拍):是时序系统中最基本的时间分段。各节拍的长度相同(一般一个节拍是一个时钟周期)。

定时脉冲(工作脉冲):有的操作如打入R,还需严格的定时脉冲,以确定在哪一刻打入。

算术逻辑运算部件

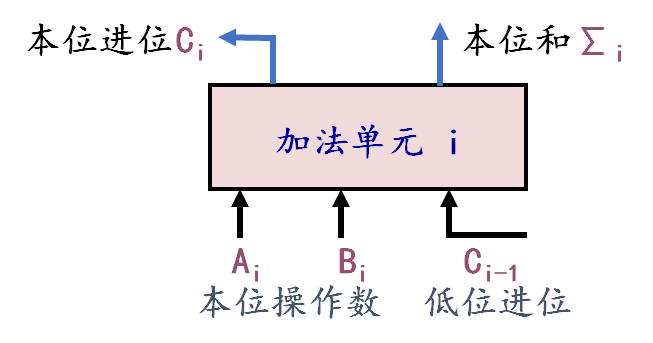

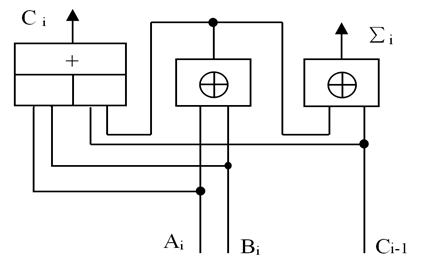

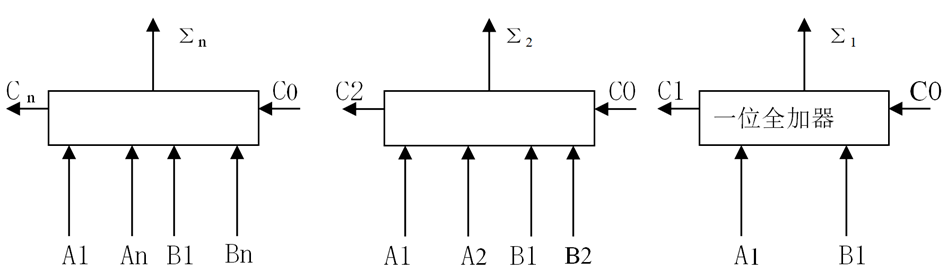

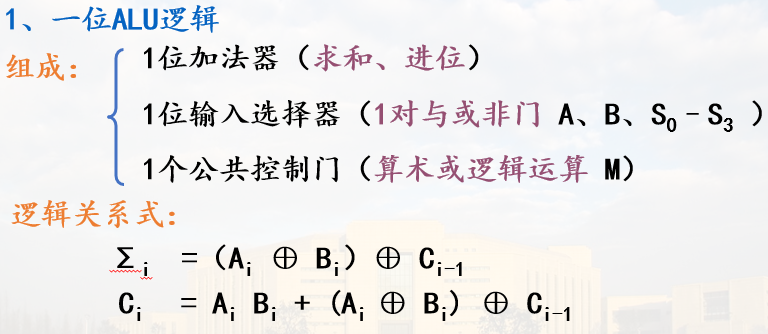

加法单元

Σi=(Ai ⊕ Bi)⊕ Ci-1

Ci = Ai Bi +(Ai ⊕ Bi)Ci-1

根据上式,得出一位全加器的逻辑电路图:

串行加法器

- 定义:如果每步只求一位和,将n位加分成n步实现,这样的加法器称为串行加法器。

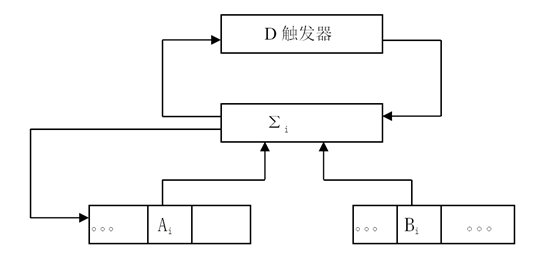

- 组成:一位全加器、移位寄存器(从低到高串行提供操作数相加)、寄存器、触发器(记录进位信号)

- 组成图:

- 特点:结构简单,速度极慢。

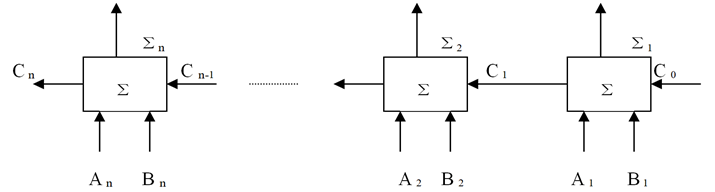

并行加法器

- 定义:如果用n位全加器一步实现n位相加,即n位同步相加,这样的加法器称为并行加法器。

- 组成:n位加法器+进位链(串行进位链、并行进位链)

根据(指Ci-1)输入量提供时间的不同,将进位链分为带串行进位链的并行加法器,带并行进位链的并行加法器。

加法器的运算速度不仅与全加器的运算速度有关,更主要的因素是取决于进位传递速度。 - 进位信号的基本逻辑

Ci = AiBi +(Ai ⊕ Bi)Ci-1

Gi = AiBi 进位产生函数(本地进位)

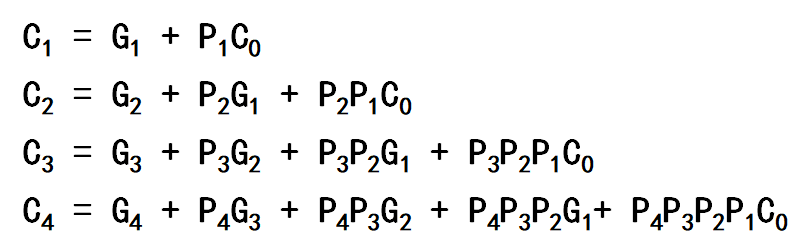

Pi = Ai ⊕ Bi 进位传递函数(传递进位) - 串行进位链

关系式:

C1 = G1 + P1C0

C2 = G2 + P2G1

……

Cn = Gn + PnGn-1

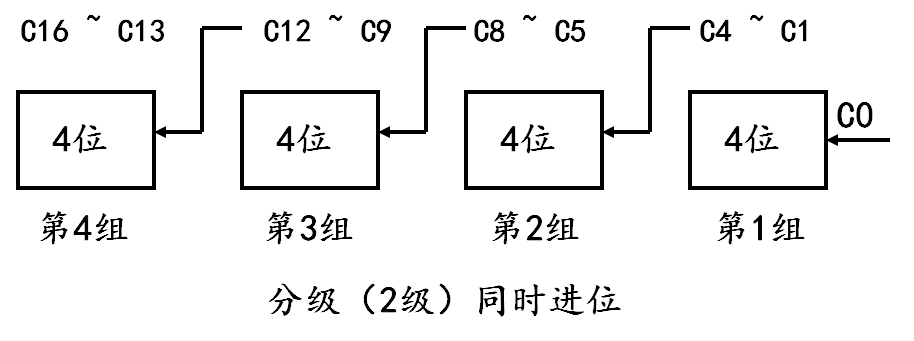

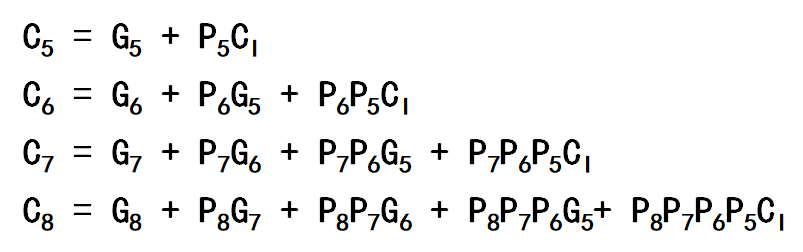

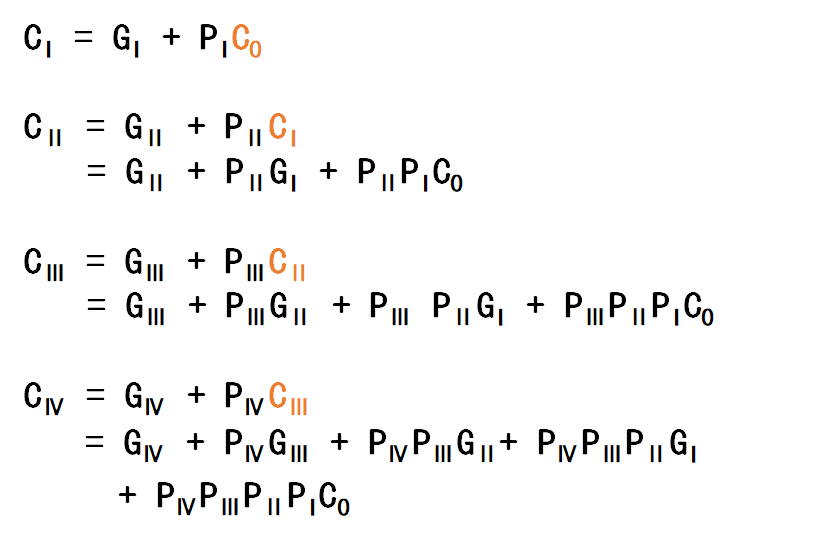

特点:结构比较简单,运算速度比较慢。 - 并行进位链

关系式:

C1 = G1 + P1C0

C2 = G2 + P2G1 + P2P1C0

……

Cn = Gn + PnGn-1 + …+ Pn…P1C0

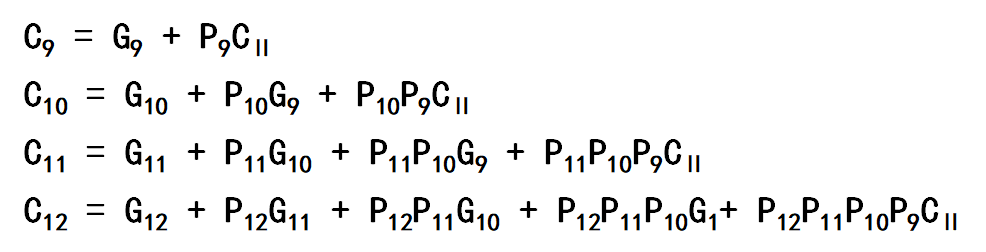

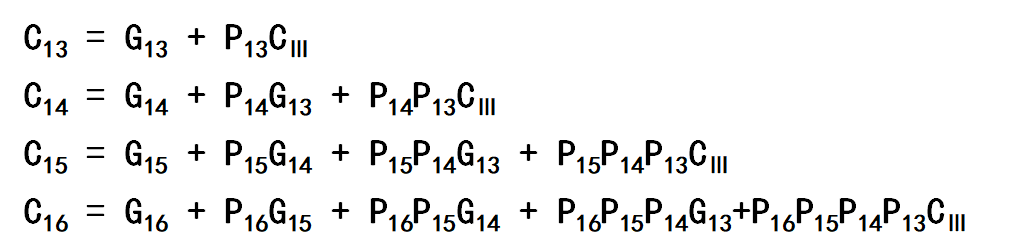

特点:结构复杂,运算速度快。 - 组内并行,组间并行(实际为串行)的进位链

分两级进行

然后

ALU单元与多位ALU部件

- 一位

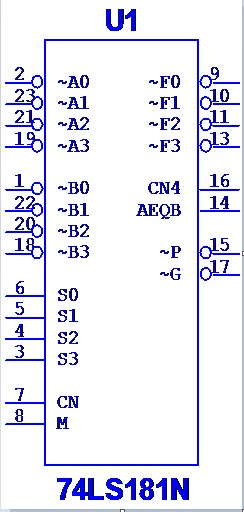

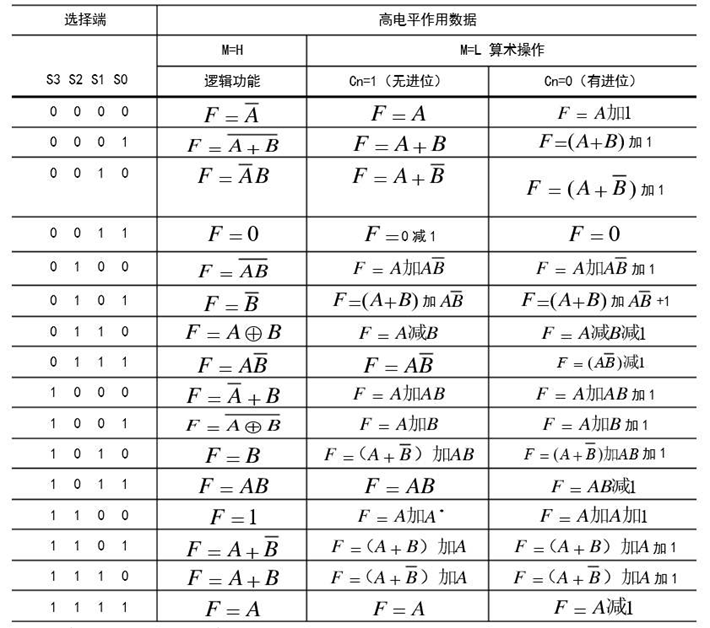

- 4位 74LK181N

其总共由22个引脚,8个数据输入端:A0、A1、A2、A3,B0、B1、B2、B3,这八个都是低电平有效。

S0、S1、S2、S3四个控制端,这四个控制端主要控制两个四位输入数据的运算,例如加、减、与、或。CN端处理进入芯片前进位值,M控制芯片的运算方式,包括算术运算和逻辑运算。

F0、F1、F2、F3是四个二进制输出端,以一个四位二进制形式输出运算的结果。CN4记录运算后的进位。

运算方法

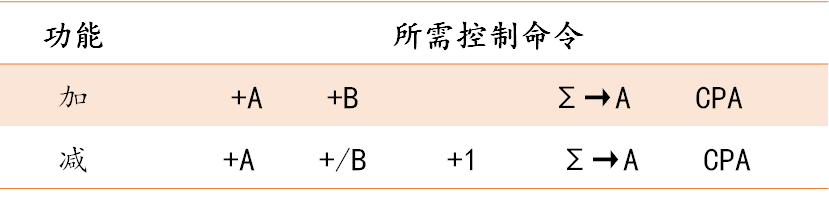

定点加减运算

两位符号位判断溢出:11正常负数,10负溢出,00正常正数,01正溢出定点乘法运算

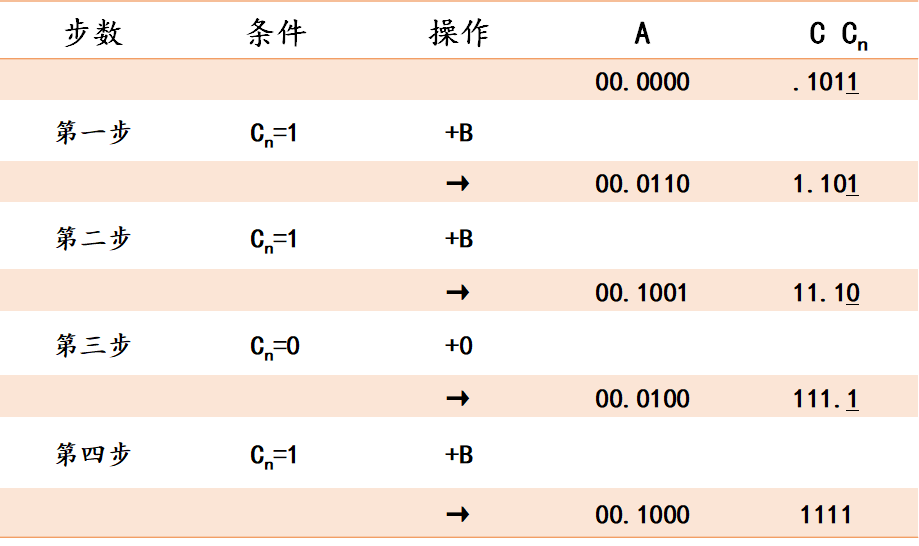

一种乘法器是将n位乘法转换为 n次累加与移位循环,因而可用常规加法器实现。 另一类乘法器结构,称为阵列乘法器(一拍内实现多项部分积相加)。 - 原码一位乘法

寄存器分配与初始值:A,B,C三个寄存器

A存放部分积累加和,初始值为0(双符号位00表示);

B存放被乘数X(绝对值),此时符号位为双符号位00(在乘的过程中,B中的值一直保持不变);

C存放乘数Y(绝对值),将符号位去掉;C寄存器的初始值是乘数Y的尾数(有效位数),以后每乘一次,将已处理的低位乘数右移舍去,同时将A寄存器的末位移入C寄存器的高位。

例:

X = 0.1101,Y =-0.1011,求 XY =? 设寄存器 A = 00.0000,B =|X|= 00.1101,C =|Y|= .1011。

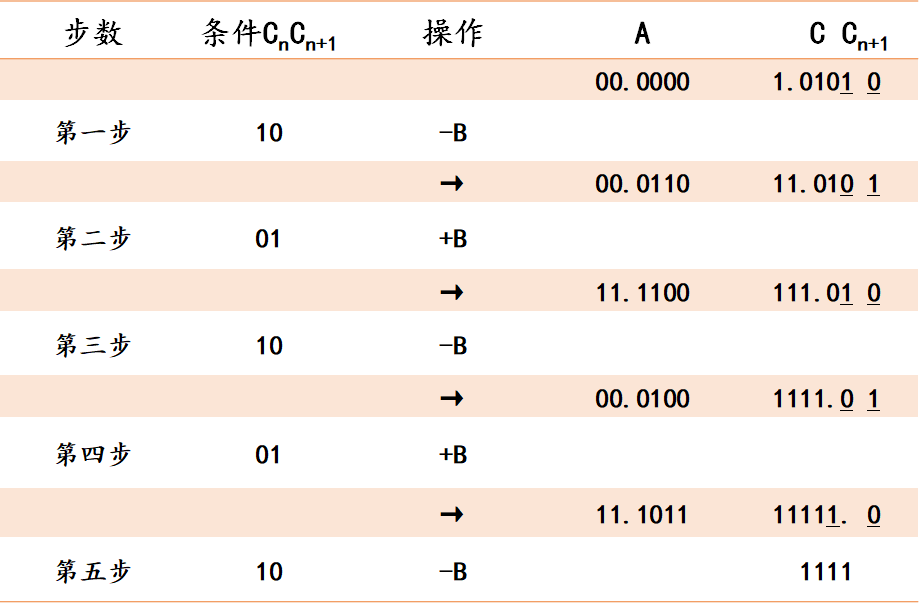

即1.10001111 - 补码一位乘法

寄存器分配与初始值:A,B,C三个寄存器

A存放部分积累加和,初始值为0(双符号位00表示);

B存放被乘数X补,(双符号位00、或11表示);

C存放乘数Y补,单符号位(符号位参与运算),Y的末位添0,称为附加位Yn+1。

例:

X = -0.1101,Y = -0.1011,求[XY]补 = ?

设 A = 00.0000,B = X补 = 11.0011,-B = -X补= 00.1101,C = Y补 = 1.0101。

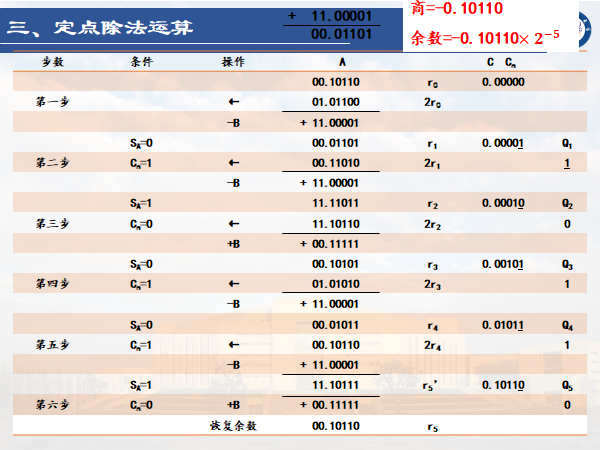

定点除法运算

A,B,C三个寄存器;

A初始值存放被除数(绝对值),以后存放各次余数,A取双符号位,从第一符号位判断是否够减,从而决定商值;

B寄存器存放除数的绝对值,取双符号位;

C存放商,取单符号位;商由末位置入,在每次置入新商时,原商同时左移一位。

基本操作与上商:

a. 第一步操作必为2r0-Y

b. 以后各部根据如下条件进行:

ri为正表示够减,即Qi=1,则第i+1步应为2ri-Y,

ri为负表示不够减,即Qi=0,则第i+1步应为2ri+Y;

c. 最后一步:若第n步(最后一步)余数为负,则需增加一步恢复余数,这增加的一步不移位,操作为rn+Y。

例:

X÷Y = -0.10110÷0.11111 = ?

设A = |X| = 00.10110,B = |Y| = 00.11111,则B = 00.11111,-B=11.00001, C = |Q| = 0.00000。

模型机的组合逻辑控制器

- 定义:组合逻辑控制器的微命令是由组合逻辑电路来实现。每种微命令都需要一组逻辑电路,全机所有微命令所需的逻辑电路就构成了微命令发生器。

- 工作原理:从主存读取的现行指令存放在IR中,其中,操作码与寻址方式代码分别经译码电路形成一些中间逻辑信号,送入微命令发生器,作为产生微命令的基本逻辑依据。微命令的形成还需考虑各种状态信息,如PSW所反映的CPU内部运行状态、由控制台(如键盘)产生的操作员控制命令、I/O设备与接口的有关状态、外部请求等等。

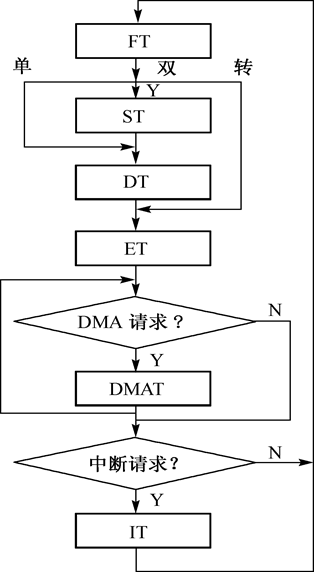

工作周期

模型机设置了六种工作周期状态,用六个周期状态触发器作为它们的标志。其中,四个工作周期(取指、源、目的、执行)用于指令的正常执行,两个工作周期(中断、DMA)用于I/O传送控制。

- 取指周期FT:在FT中完成的操作是公共性操作;

- 源周期ST——如果需要从主存中读取源操作数(非寄存器寻址),则进入ST。

- 目的周期DT——如果需要从主存中读取目的地址或目的操作数(非寄存器寻址),则进入DT。

- 执行周期ET——取得操作数后,CPU进入ET,这也是各类指令都需经历的最后一个工作阶段。

- 中断周期IT——除了考虑指令的正常执行,还需考虑外部请求带来的变化。在响应中断请求之后,到执行中断服务程序之前,需要一个过渡期,称为中断周期IT。

- DMA周期DMAT——响应DMA请求之后,CPU进入DMAT。在DMAT中,CPU交出系统总线的控制权,即MAR、MDR与系统总线断开(呈高阻态),改由DMA控制器控制系统总线,实现主存与外围设备间的数据直传。

指令周期与操作时间表

拟定各类指令的执行流程,也就是确定指令执行的具体步骤,即各类信息如何分步地按要求流动。拟定操作时间表,即给出实现上述流程所需的微操作命令序列。其中包含维持一个时钟周期的电位型微命令,以及短暂的脉冲型微命令。操作时间表还将表明出现各种微命令的逻辑条件与时间条件。