CPU概述

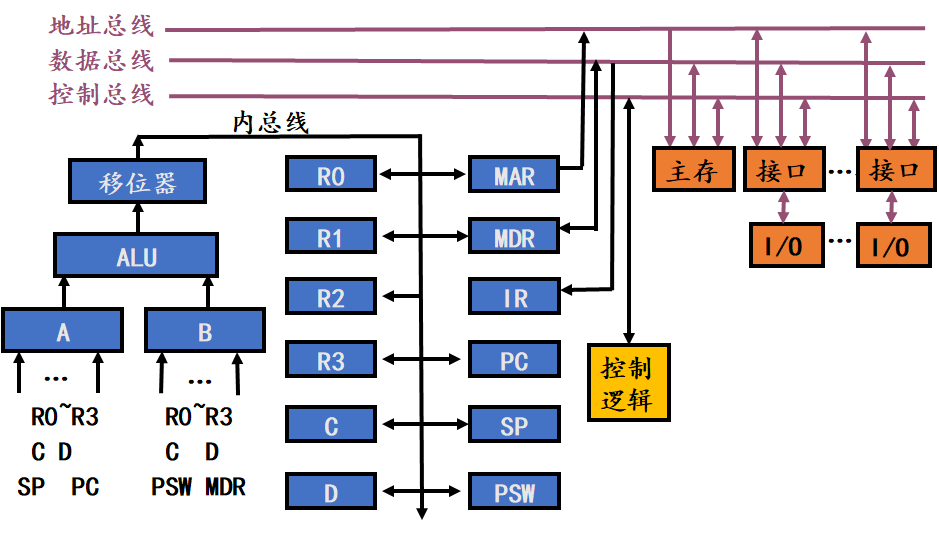

CPU基本包含运算部件、缓存部件、寄存器组、微命令产生部件(控制部件)、时序系统、数据/控制通路

总体来看CPU的工作过程就是

- 从主存(或缓存)中读取命令,

- 将指令放入指令寄存器(IR),

- 然后对指令译码,把指令分解成一系列的微操作,

- 再发出各种相应的控制命令,控制各功能部件执行相关操作,

从而完成一条指令的执行,实现对应的功能。运算部件

ALU(算术逻辑运算单元)是核心、主要由加法器构成缓存部件

为提高CPU处理主存数据的效率而设寄存器组

一般分为(8)

- 通用寄存器组

- 暂存器

- IR指令寄存器

- PC程序计数器

- PSW程序状态寄存器

- MAR地址寄存器

- MBR/MDR数据缓冲寄存器

- SP堆栈指针寄存器

具体可见

- 可编程寄存器

R0~R3通用寄存器(000,001,010,011)、SP(100)堆栈指针、PSW(101)程序状态寄存器、PC程序计数器 - 指令寄存器IR

用来存放现行运行指令,它的输出是产生微操作命令序列的主要逻辑依据。 - 暂存器

C、D约定从主存中读源操作数、操作数地址时用C;从主存中取目的操作数、操作数地址或暂存时,用D - 主存接口寄存器MAR、MDR(MBR)

- 节拍是执行一步的所需时间(一个周期可以由多个节拍)

- 时序控制方式:

指令系统

指令集有CISC(复杂指令集计算机)RISC(精简指令集计算机)

按地址结构可分为:三地址指令、二地址指令、一地址指令、零地址指令

操作码结构多设为可变字长指令

寻址

指令的功能和类型

现在大部分微机将指令分为;

- 传输类指令

- 访存指令

- I/O指令

- 算术运算指令

- 逻辑运算指令

- 程序控制类指令

- 处理机控制类指令

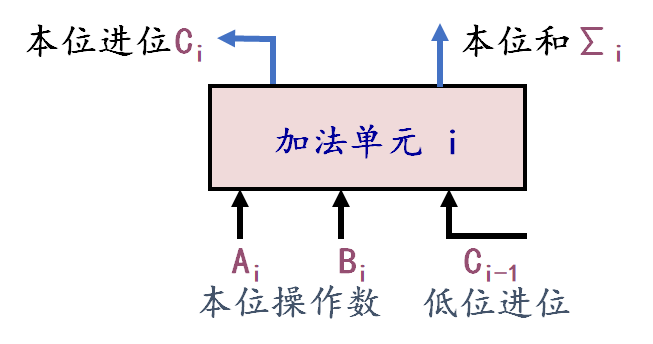

加法器与运算部件

加法器及其进位逻辑

Σi =(Ai ⊕ Bi)⊕ Ci-1

Ci = Ai Bi +(Ai ⊕ Bi)Ci-1 - 串行加法器:如果每步只求一位和,将n位加分成n步实现

- 并行加法器:如果用n位全加器一步实现n位相加,即n位同步相加

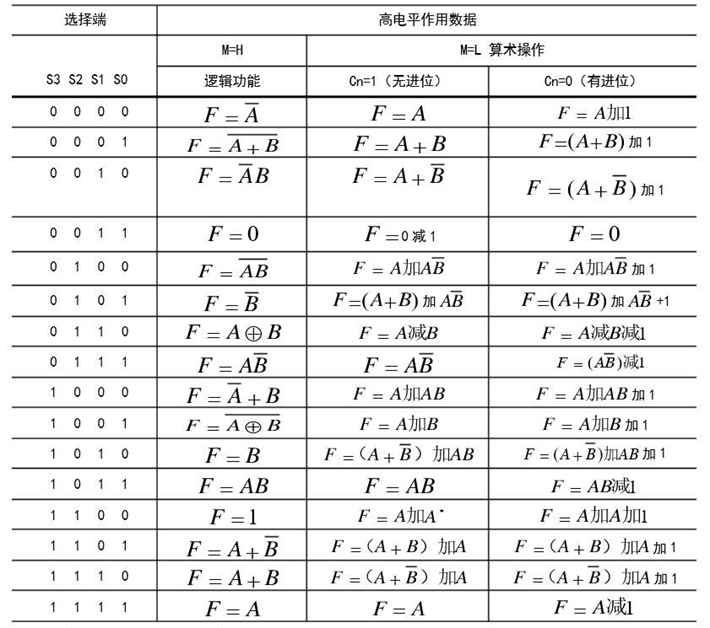

- 数据通路操作

- ALU输入选择

- ALU功能选择

- 移位器功能选择

- CPU内部总线结果分配控制信号

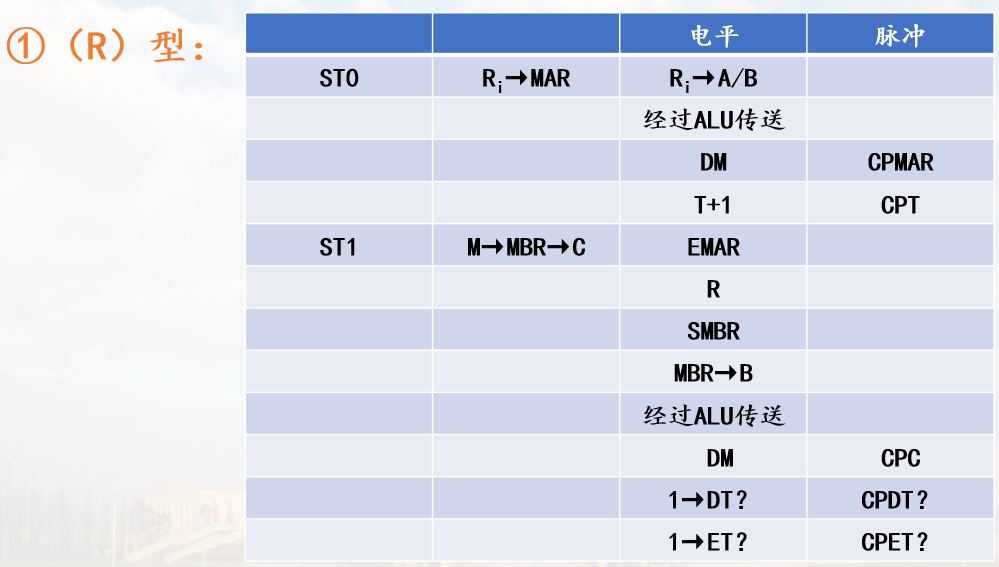

- 访存操作相关控制信号

EMAR地址使能

R/W控制主存读写模式

EMDR数据使能

SMDR打入(把数据总线上的数据置入寄存器MDR)

SIR读指令写入

(W和EMDR基本绑定)

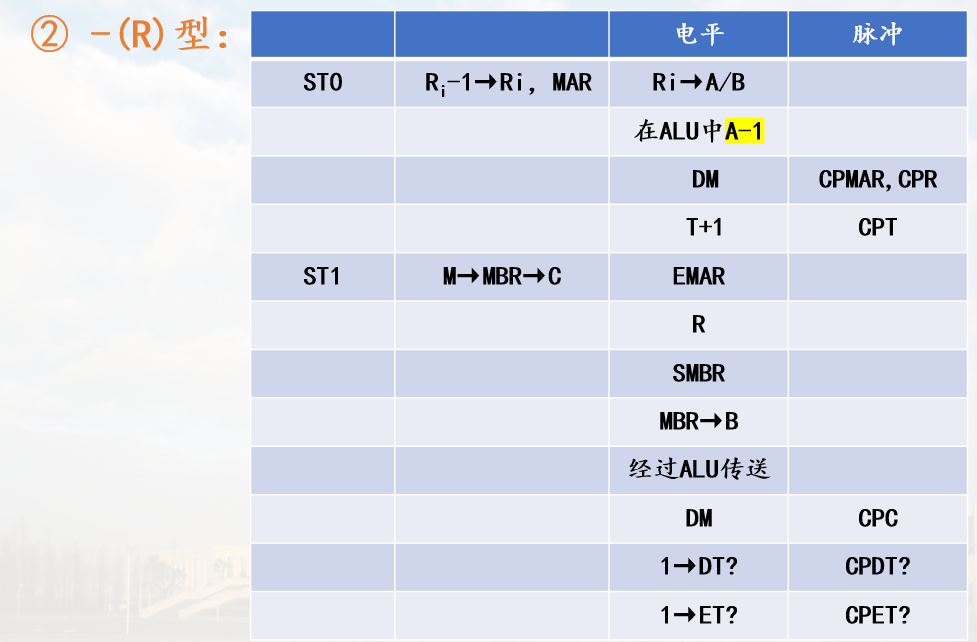

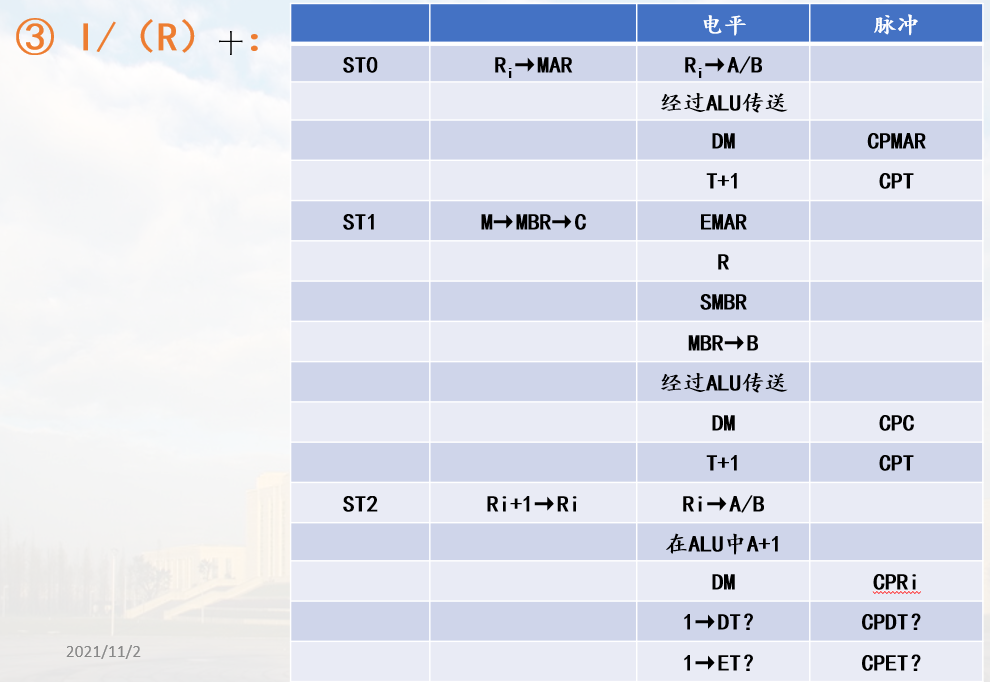

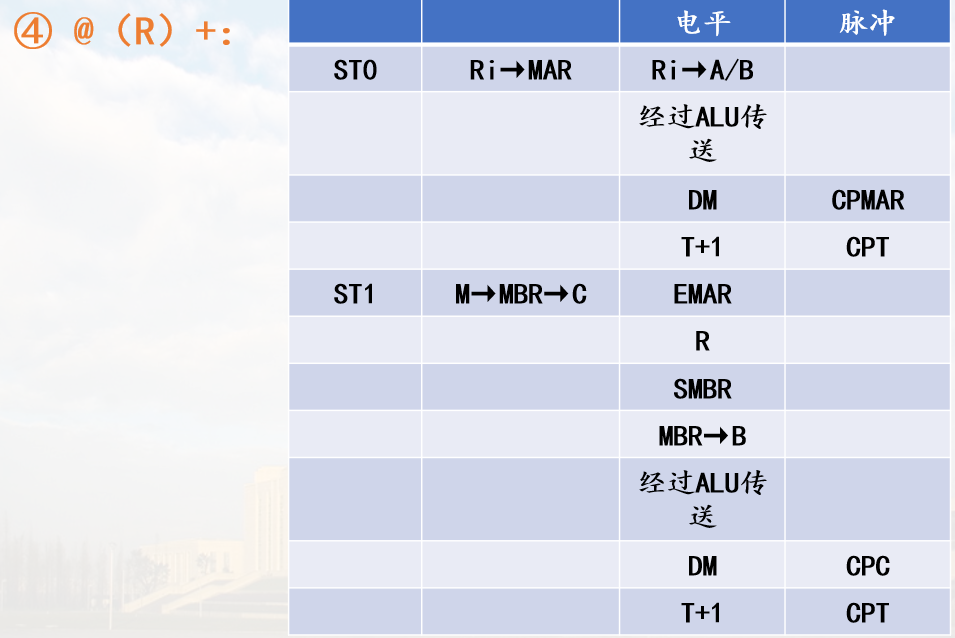

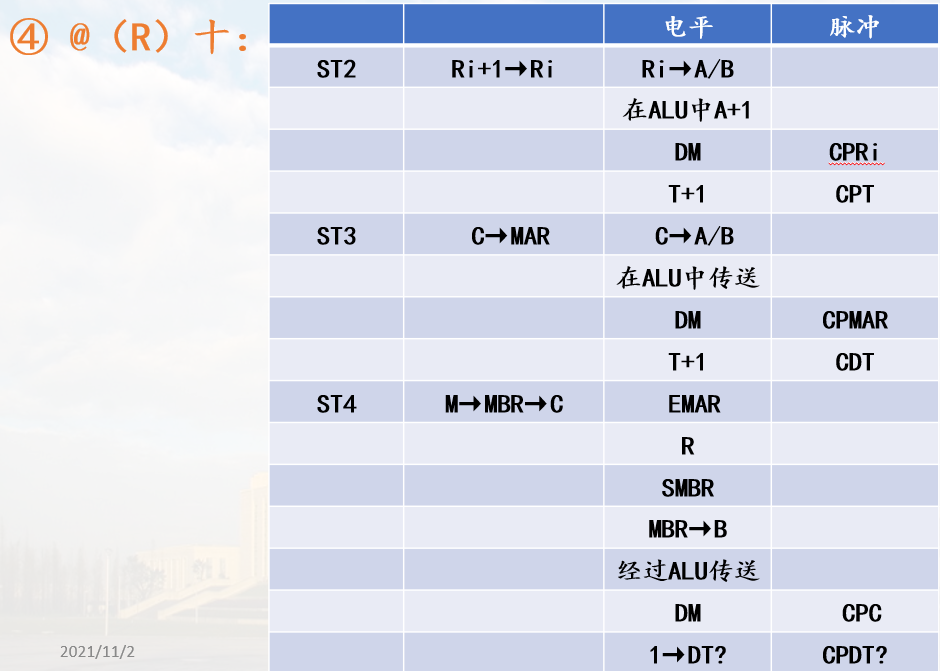

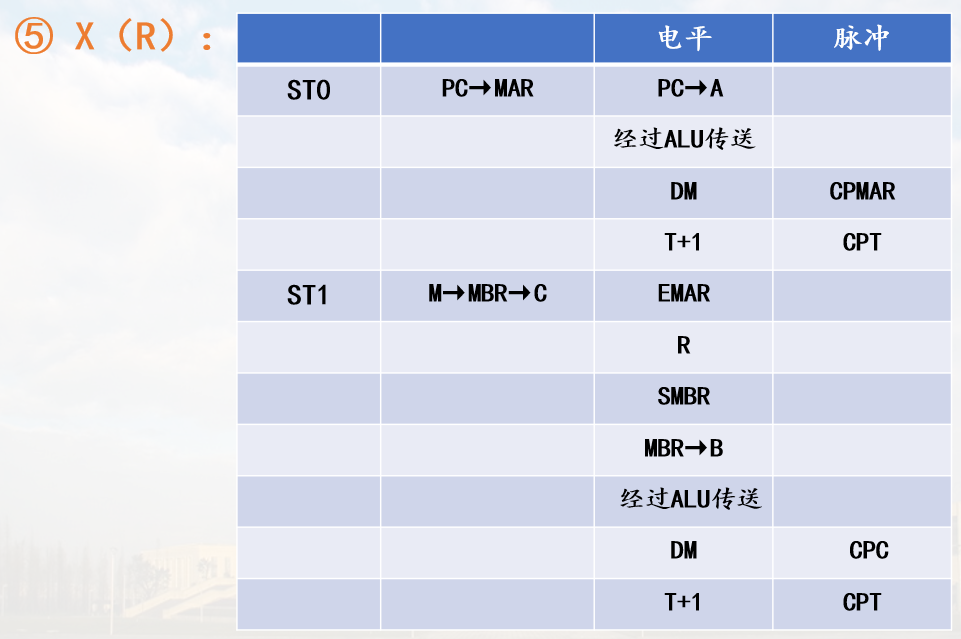

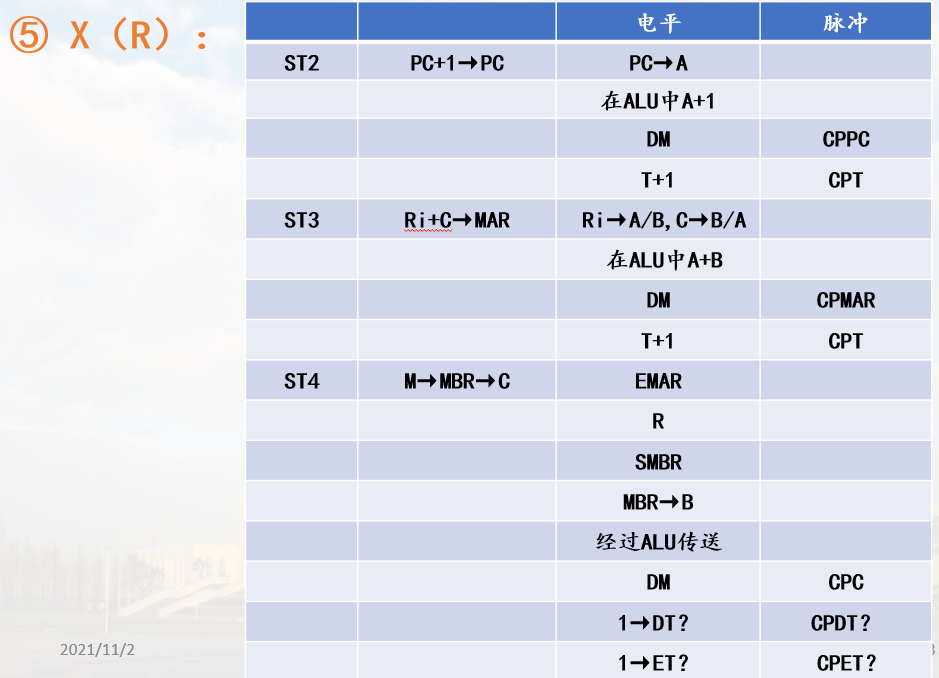

又分四个基本执行阶段:取指令FT、源操作ST、目的操作DT、执行ETMOV指令重点

组合逻辑控制

insert切换输入模式(鼠标光标横竖)